#### THINKING MACHINES CORPORATION

.

.

.

### CONNECTION MACHINE TECHNICAL SUMMARY

The Connection Machine System

# **Connection Machine Model CM-2 Technical Summary**

Version 6.0 November 1990

Thinking Machines Corporation Cambridge, Massachusetts

First printing, November 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Thinking Machines Corporation. Thinking Machines Corporation reserves the right to make changes to any products described herein to improve functioning or design. Although the information in this document has been reviewed and is believed to be reliable, Thinking Machines Corporation does not assume responsibility or liability for any errors that may appear in this document. Thinking Machines Corporation does not assume any liability arising from the application or use of any information or product described herein.

Connection Machine<sup>®</sup> is a registered trademark of Thinking Machines Corporation. CM-1, CM-2, CM-2a, CM, and DataVault are trademarks of Thinking Machines Corporation. C\*<sup>®</sup> is a registered trademark of Thinking Machines Corporation. Paris, \*Lisp, and CM Fortran are trademarks of Thinking Machines Corporation. C/Paris, Lisp/Paris, and Fortran/Paris are trademarks of Thinking Machines Corporation. VAX, ULTRIX, and VAXBI are trademarks of Digital Equipment Corporation. Symbolics, Symbolics 3600, and Genera are trademarks of Symbolics, Inc. Sun, Sun-4, SunOS, and Sun Workstation are registered trademarks of Sun Microsystems, Inc. UNIX is a registered trademark of AT&T Bell Laboratories. The X Window System is a trademark of Storage Technology Corporation. Trinitron is a registered trademark of Sony Corporation.

Copyright © 1990 by Thinking Machines Corporation. All rights reserved.

Thinking Machines Corporation 245 First Street Cambridge, Massachusetts 02142–1264 (617) 234–1000/ 876–1111

## Contents

## Part I The Parallel Environment

| Chapter 1 | Parallel Architecture                      | 3  |

|-----------|--------------------------------------------|----|

| 1.1       | System Organization                        | 3  |

| 1.2       | Data Parallel Hardware                     | 4  |

| 1.3       | Data Parallel Computation                  | 7  |

| 1.4       | 1.4 Data Parallel Software                 |    |

| Chapter 2 | The Operating System Environment           | 13 |

| 2.1       | The Front-End Environment                  | 13 |

| 2.2       | Partitioning the Connection Machine System | 14 |

| 2.3       | The NQS Batch System                       | 15 |

| 2.4       | Timesharing                                | 17 |

| 2.5       | The Program Development Environment        | 17 |

| 2.6       | The Program Execution Environment          | 18 |

| 2.7       | The Connection Machine File System         | 19 |

| 2.8       | CM Diagnostics                             | 20 |

## Part II Parallel Software

| Chapter 3 | Languages                                 | 23 |

|-----------|-------------------------------------------|----|

| 3.1       | Establishing Parallel Data Structures     | 24 |

| 3.2       | Establishing Linkages among Data Elements | 24 |

| 3.3       | Establishing Scalar Data                  | 25 |

| 3.4       | Operations on Mixed Data                  | 25 |

| 3.5       | Conditionals                              | 25 |

|   | Chapter 4 | Fortran                                 | 27 |

|---|-----------|-----------------------------------------|----|

|   | 4.1       | Structuring Parallel Data               | 27 |

|   | 4.2       | Computing in Parallel                   | 29 |

|   | 4.3       | Communicating in Parallel               | 30 |

|   | 4.4       | Transforming Parallel Data              | 32 |

|   | 4.5       | To Learn More                           | 33 |

|   | Chapter 5 | The C* Language                         | 35 |

|   | 5.1       | Structuring Parallel Data               | 35 |

|   | 5.2       | Computing in Parallel                   | 37 |

|   | 5.3       | Communicating in Parallel               | 38 |

|   | 5.4       | Transforming Parallel Data              | 40 |

|   | Chapter 6 | The *Lisp Language                      | 41 |

|   | - 6.1     | Structuring Parallel Data               | 42 |

|   | 6.2       | Computing in Parallel                   | 45 |

|   | 6.3       | Communicating in Parallel               | 46 |

|   | 6.4       | Transforming Parallel Data              | 48 |

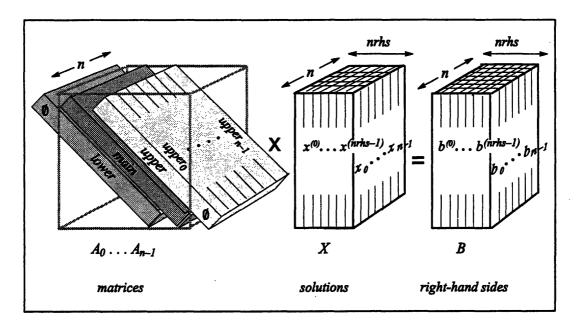

|   | Chapter 7 | CM Scientific Software Library          | 51 |

|   | 7.1       | CMSSL Capabilities                      | 51 |

|   | 7.2       | CMSSL Parallel Computation              | 53 |

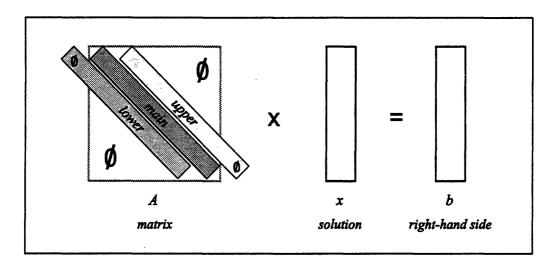

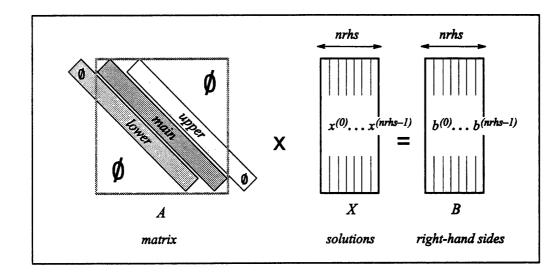

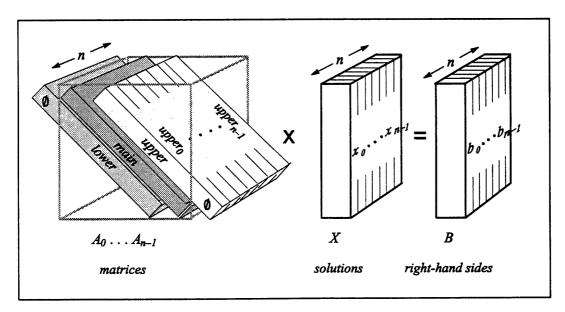

|   | 7.3       | Linear Algebra                          | 56 |

|   | 7.4       | Fast Fourier Transforms                 | 58 |

|   | 7.5       | Random Number Generators                | 59 |

|   | 7.6       | Statistical Analysis                    | 60 |

|   | Chapter 8 | Data Visualization                      | 61 |

|   | 8.1       | Visualization Output from the CM System | 62 |

|   | 8.2       | *Render                                 | 63 |

| • | 8.3       | Generic Display Interface               | 65 |

|   | 8.4       | Image File Interface                    | 67 |

7

## Part III Parallel Architecture

| Chapter 9  | 9 Paris                                |           |

|------------|----------------------------------------|-----------|

| 9.1        | Virtual Machine Architecture           | 71        |

| 9.2        | Instruction Set Overview               | 75        |

|            |                                        |           |

| Chapter 10 | CM-2 Architecture                      | 81        |

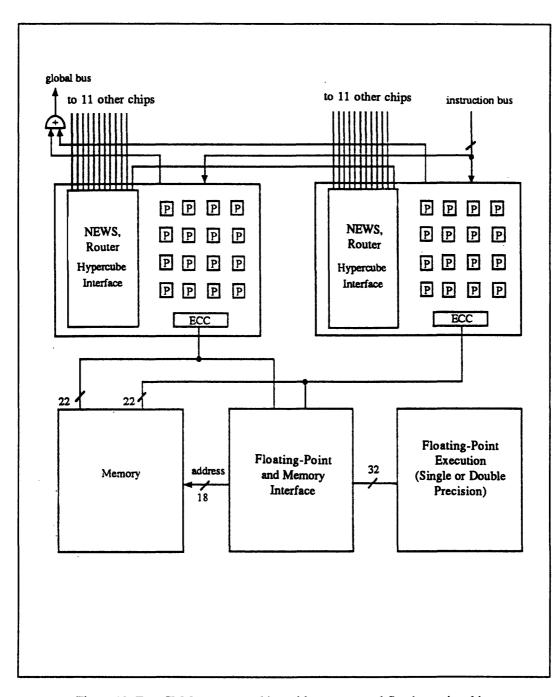

| 10.1       | Processor Architecture                 | 83        |

| 10.2       | The Parallel Processing Array          | 83        |

| 10.3       | The Floating-Point Accelerator         | 85        |

| 10.4       | The Router                             | 86        |

| 10.5       | The NEWS Grid                          | 88        |

| 10.6       | Scans and Spreads                      | 89        |

| 10.7       | Communication with the Front End       | 90        |

|            |                                        |           |

| Chapter 11 | Data and Image I/O                     | 91        |

| 11.1       | Data I/O Channels                      | 91        |

| 11.2       | Data I/O Overview                      | 92        |

| 11.3       | Graphics Output for Data Visualization | 93        |

| 11.4       | CM I/O Controller                      | 93        |

| 11.5       | CMIO Bus                               | 94        |

|            |                                        |           |

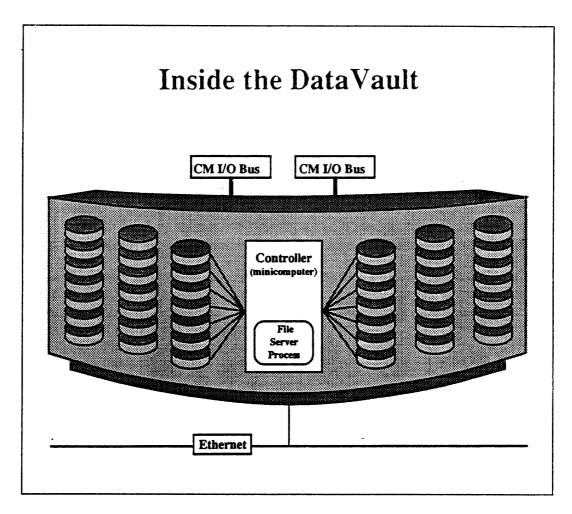

| Chapter 12 | The DataVault                          | 97        |

| 12.1       | The File Server                        | <b>99</b> |

| 12.2       | Writing and Reading Data               | 100       |

| 12.3       | Data Protection                        | 101       |

|            |                                        |           |

| Chapter 13 | CMIO Intelligent Bus Interfaces        | 103       |

| 13.1       | HIPPI Bus Interface                    | 103       |

| 13.2       | VMEbus Interface                       | 104       |

| 13.3       | SCSI Bus Interface                     | 105       |

|            |                                        |           |

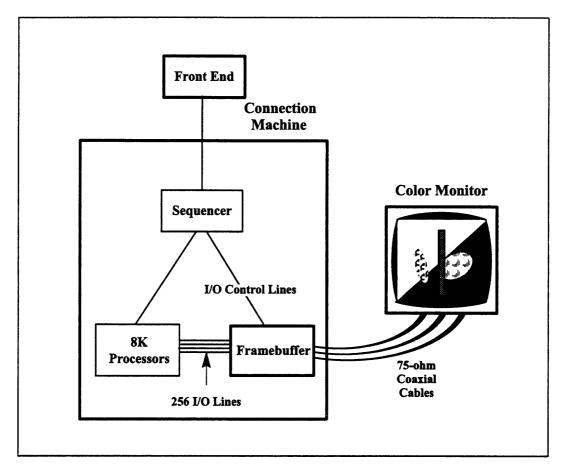

| Chapter 14 | The Graphics Display System            | 107       |

| 14.1       | Connection Machine Framebuffer         | 107       |

| 14.2       | The Monitor                            | 109       |

V

vi

.

## Connection Machine Model CM-2 and DataVault System

The Connection Machine Model CM-2 uses thousands of processors operating in parallel to achieve peak processing speeds of above 10 gigaflops. The DataVault mass storage system stores up to 60 gigabytes of data.

# Part I The Parallel Environment

.

.

2,

# Chapter 1 Parallel Architecture

The Connection Machine Model CM-2 is a data parallel computing system. Data parallel computing associates one processor with each data element. This computing style exploits the natural computational parallelism inherent in many data-intensive problems. It can significantly decrease the execution time of a problem, as well as simplify its programming. Execution time is frequently reduced in proportion to the number of data elements in the computation; programming effort is reduced in proportion to the complexity involved in expressing a naturally parallel problem statement in a serial manner.

The Connection Machine Model CM-2 is an integrated system of hardware and software. The hardware elements of the system include front-end computers that provide the development and execution environments for the users' software, a parallel processing unit of 64K processors that executes the data parallel operations, and a high-performance data parallel I/O system. Software elements begin with the standard operating system and program development environment of the front-end computer and enhance that environment with extensions to standard languages and tools that facilitate data parallel program development. Users write programs using familiar languages and constructs, taking advantage of the full, enhanced front-end development environment. When they choose, they can also call on CM language features and library routines specifically designed to handle tasks and problems germane to large-scale data-intensive programming. Programs have normal sequential control flow; new synchronization structures are not needed. Thus, users can easily develop programs that exploit the power of the Connection Machine hardware.

## 1.1 System Organization

The Connection Machine system was specifically designed to handle the largest computational problems. At the heart of any large computational problem is its data set: some combination of related data objects, such as numbers, characters, records, structures, and arrays. The task of any application is to select, combine, rearrange, and operate upon this data. Data-level parallelism expedites this task by taking advantage of the parallelism inherent in large data sets.

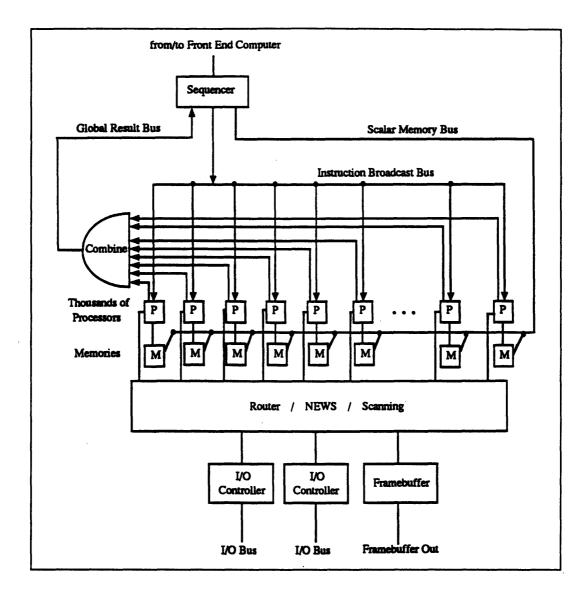

At the heart of the Connection Machine system is the parallel processing unit, which consists of up to 64K processors, each with up to 128 kilobytes of memory. These processors can not only process the data stored in their memory, but also can exchange information among themselves and with I/O peripherals. All these operations happen in parallel on all processors.

A CM-2 parallel processing unit may contain 16K, 32K, or 64K data processors. The model CM-2a may contain 4K or 8K data processors. Here, and throughout this document, "K" stands for 1024, or 2<sup>10</sup>. Thus 64K means 65,536; 32K means 32,768; 16K means 16,384; 8K means 8,192; and so on.

The Connection Machine processors are used whenever an operation can be performed simultaneously on many data objects. Data objects remain in the Connection Machine memory during execution of the program and are operated upon in parallel. This model differs from the serial model, where data objects in a computer's memory are processed one at a time, by reading each one in turn, operating on it, and then storing the result back in memory before processing the next object.

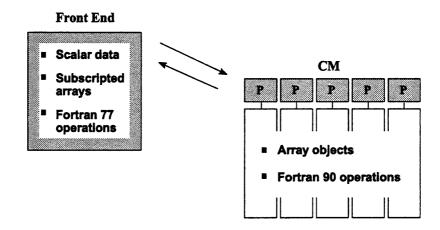

Of course, some small part of an application's data may be better processed serially. Such data resides in the memory of the front-end computer and is processed serially in the usual way. The memories of the parallel processors hold the bulk of data that can be usefully processed in parallel. The flow of control is handled entirely by the front end, including storage and execution of the program and all interaction with the user and/or programmer. Parallel data is operated upon through commands sent by the front end to the Connection Machine processors.

## **1.2 Data Parallel Hardware**

The Connection Machine system implements data parallel programming constructs directly in hardware and microcode. Parallel data structures are spread across the data processors, with a single element stored in each processor's memory. When parallel data structures contain more data elements than the system has processors (the normal situation), the system operates in virtual processor mode, presenting the user with a larger number of processors, each with a correspondingly smaller memory. This allows the user to write programs assuming the number of processors that is natural for the application, rather than forcing code to conform to the number of hardware processors available. Each hardware processor is made to simulate the appropriate number of virtual processors; as the program issues each parallel instruction, microcode causes it to be executed many times, once for each virtual processor. The same program can run without change on different quantities of hardware processors—but the more hardware, the faster it runs.

Interprocessor communication is implemented by a special-purpose high-speed network. When data is needed, it is passed over the network to the appropriate processors. Processors that hold interrelated data elements store pointers to one another, thus supporting completely general patterns of communication. In addition, special hardware supports certain commonly used regular patterns of communication. Nearest-neighbor communication in a multidimensional rectangular grid is particularly efficient.

High-speed transfers between peripheral devices and Connection Machine memory take place through the Connection Machine I/O system. All processors, in parallel, pass data to and from I/O buffers. The data is then moved between the buffers and the peripheral devices. Connection Machine high-speed peripherals include the DataVault mass storage system, the Connection Machine graphics display system, the Connection Machine VME I/O system, and the HIPPI high-speed interface.

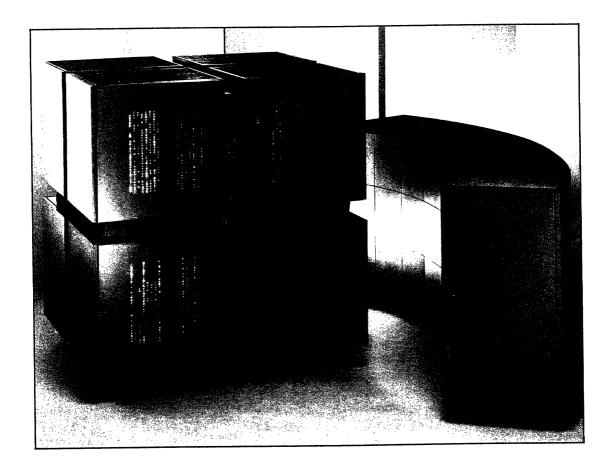

Figure 1. Components of a Connection Machine system. The user's terminal provides access to the front-end computer, CM-2 parallel processing unit, DataVaults, and high-resolution graphics color monitors.

6

## **1.3 Data Parallel Computation**

Connection Machine systems are designed to operate on large amounts of data. These data sets may be richly interconnected or totally autonomous. A scientific simulation data set, such as a finite-element grid, is highly interconnected, with every node value connected to several element values and vice versa. Disparate values are continually being brought together, computed on, and redispersed. A document data base, on the other hand, may be totally autonomous. The search of any one document proceeds entirely without reference to any of the others. There is no need to combine information from multiple documents in a single computation.

The Connection Machine system is made up of large numbers of processors, each with its own local memory. (Note that a system with 65,536 processors, each with a 128-kilobyte memory, has a total of 8 gigabytes of physical memory.) From the programming perspective, it is possible to think of the memory in either of two ways. When computing on interconnected data sets, it is easiest to think of the memory as a single multi-gigabyte data space. When computing on autonomous data, it is easiest to think of it as many local memories.

Efficient Connection Machine algorithms invariably combine both points of view. When data is being being gathered, it is done in the global context. Once the data is gathered, however, it becomes local data. The ensuing computations are then most easily thought of as being carried out in multiple local memories.

#### **Physical Processors and Memory**

The unit of data in a Connection Machine is the parallel variable. A parallel variable is not a new concept; all Fortran arrays, for example, are parallel variables. The array A(64000)is a parallel variable with 64,000 individual data elements. The array D(1000, 1000) is a parallel variable with 1,000,000 data elements. What is important in the Connection Machine system is the way such variables are allocated into physical memory. They are not allocated contiguously in the 8-gigabyte global memory space, because to do so would bunch the variables up in the local memories of the first few processors. Instead, individual arrays are spaced out through the whole address space, so that each processor's local memory space receives the same amount of data. If the number of elements in the array matches the number of physical processors, then each local memory receives one element. If three arrays, such as A(64000), B(64000), and C(64000) are defined on a 64K CM-2, then space will be allocated in each local memory for one instance of each variable. Initialization of these arrays may proceed in either of two ways. The following sequence of Fortran 77 code initializes one element at a time, and hence requires 64,000 units of time:

DO 20 I = 1,64000 20 A(I) = 4

An exactly equivalent Fortran 90 statement performs the same initialization in a single unit of time:

$$A = 4$$

A = 4 is a parallel command, and executes for all the elements of A (in this case, for 64,000 such elements). On the Connection Machine system, this parallel form is vastly more efficient than its serial counterpart. Initialization of a parallel array to a constant value is carried out by broadcasting the constant from the front end to all the processors at once.

Initialization to a constant is always a local operation. Other computations may or may not be local. An example of a local addition in Fortran would be:

DO 20 I = 1, 64000 20 C(I) = A(I) + B(I)

Such a computation proceeds serially, but at each step, the appropriate values of  $\mathbf{A}$  and  $\mathbf{B}$  are to be found in the same local processor, along with the location of  $\mathbf{C}$  into which the sum is to be stored. Such a program sequence also has a vastly more efficient parallel form on the Connection Machine:

C = A + B

#### **Virtual Processors**

The Connection Machine hardware allows each physical processor to operate as many virtual processors, each with a smaller memory. The virtual memory facility is invoked automatically when a parallel variable is declared. Thus the declaration

DIMENSION D(1000,1000), E(1000,1000), F(1000,1000)

causes the compiler (in this case the Fortran compiler, but other languages have corresponding ways of declaring parallel variables) to invoke a million virtual processors. The way this invocation is carried out depends on the physical hardware configuration at run time. If there are 65,536 processors available, then each is subdivided 16 ways. (Note that 65,536 times 16 is 1,048,576 virtual processors, slightly more than are needed.) Thus the two statements

C = A + BF = D + E

are equally valid parallel statements. Assuming the declarations shown above, the first statement will execute in one unit of time on a 64K CM-2. One unit of time, however, is only enough to do one sixteenth of the second statement. The system automatically cycles fifteen more times to complete the second statement.

Because of the virtual processor capability, these parallel statements also execute on smaller CM-2 or CM-2a systems. On an 8K CM-2a with one gigabyte of memory, the array declaration **A** (64000) invokes 8 virtual processors per physical processor; the declaration **D** (1000,1000) invokes 128 virtual processors. Virtual processors allow CM-2 programs to be completely scalable. They run unchanged on larger and smaller configurations, because the underlying virtual processor configuration changes dynamically to match the code to the hardware resource. When arrays of different sizes are used in the same program (as they typically are) the system changes its virtual processor context as needed to match the current data being operated on.

#### **Global Operations**

Global operations are directly supported in hardware just as local operations are. A typical global operation is:

$$X = MAX(A)$$

where X is a scalar (as opposed to a parallel) variable. All the values of A are compared, and the largest is stored in X. This is an example of a *reduction* operation; a large set of values is reduced to a scalar result. Other reduction operations include summation, logical AND, and logical OR.

#### Parallel Computation on Interconnected Data Structures

So far we have seen cases where there is no connection between data elements (local computation) and cases where there is total connection between data elements (global reduction). The more typical case lies in between. The inherent structure of most data sets links each data element to some, but not all of the others. Often the linkages are to neighboring elements, so the structure is localized (but not in the absolute sense of "local" used in the previous section). A matrix, for example, is generally thought of as having row and column structure. Elements that have one subscript the same are used in a connected way. If the matrix is used as part of a finite-difference calculation, then the horizontal and vertical neighbors are continually being brought together for computation. If a data structure is converted from the spatial domain to the frequency domain, then a butterfly topology may be invoked during the course of a Fast Fourier Transform (FFT).

It is not possible to arrange interconnected data so that all the pieces of data will reside in the processors that need to use them, because the same piece of data must be used in more than one part of the computation, by more than one processor. Interprocessor communication is required. Computations on data structures have a definite rhythm: first data elements are brought together, then computations are performed. Once the data elements have been brought together, the computations are local. Even on very complex data structures, it is possible to have most of the interacting elements located in the same processor memory. Typically, only a few need to be brought in from another processor's memory.

#### Localized, Regular Structures

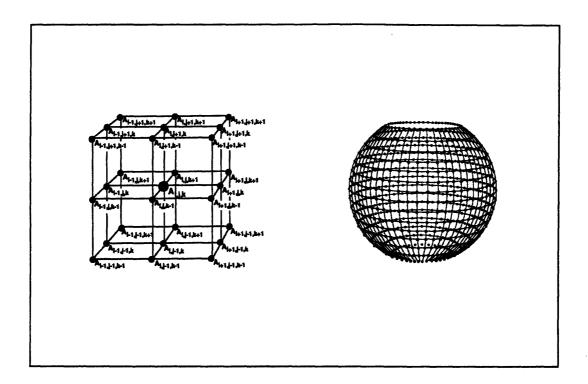

In a localized, regular data structure, the pattern of interconnection is the same everywhere in the data structure, and the paths between interconnected data elements are very short. A finite difference grid is a very typical example. Each data element is connected to its neighbors to the north, south, east, and west. In the three-dimensional case, it is also connected front and back. When the data structure is originally set up, one element of the array is stored in the local memory of each processor.

The CM-2 hardware includes specific communications hardware, the NEWS grid, that supports nearest-neighbor communications on multidimensional rectangular grids. Each Connection Machine language has facilities for moving data along the NEWS grid. A computation on a regular data structure alternates between the gathering of data on the NEWS grid and performing computations locally in the individual processors.

Figure 2. Examples of regular grid structures

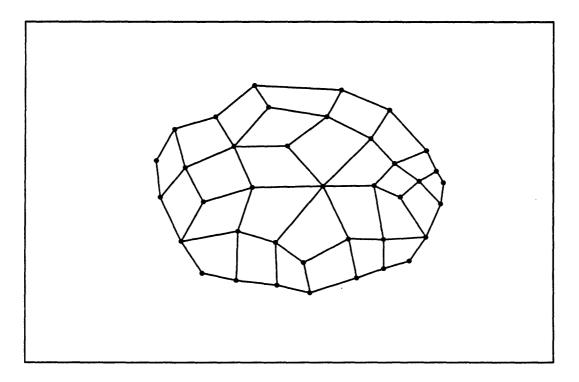

Figure 3. Example of an irregular grid structure

#### **Irregular and Global Structures**

In an irregular data structure, the pattern of interconnection varies from one part of the the data to another. Most irregular data structures are relatively localized, but it is also possible to have interconnections between very distant data elements. A finite-element data structure is a common example of a local, irregular pattern. Each of the parallel languages includes language constructs to bring data together and to scatter it back out. Once the appropriate data elements are brought together, the computations on them are carried out in the individual processors.

## **1.4 Data Parallel Software**

To expedite the handling of parallel data structures, Connection Machine system software offers languages that provide data parallel extensions to well-known standards and libraries that facilitate specialized tasks in scientific computing and visualization. It also provides a UNIX-based operating system and various networking capabilities. In all cases, system software is integrated with existing programming languages and environments, so that users can rapidly feel at home on the system.

Fortran on the Connection Machine system is based on Fortran 77 but also uses the array extensions in the draft Fortran 90 standard (proposed by ANSI technical committee X3J3) to express data parallel operations. These array extensions map naturally onto the underlying data parallel hardware.

The C\* language, developed by Thinking Machines Corporation, is a data parallel extension of the C programming language (ANSI technical committee X3J11). C\* programs are similar in style to C programs; the extensions are unobtrusive and easy to learn. Parallel code looks like serial code, but is executed in all parallel processors simultaneously.

The \*Lisp language, also developed by Thinking Machines Corporation, is a data parallel dialect of Common Lisp (a version of Lisp currently being standardized by ANSI technical committee X3J13). \*Lisp gives programmers fine control over the CM-2 hardware while maintaining the flexibility of Lisp.

Chapters 2 through 8 of this Technical Summary examine this software environment. Chapters 9 through 14 then discuss the architecture that supports it.

## Chapter 2

## **The Operating System Environment**

The Connection Machine Operating System (CM OS) is fully compatible with the UNIX operating system and enhances it in an intuitive manner. The X Window System environment is also fully supported. Since the CM OS follows UNIX standards for its file system and works with UNIX, VME, and HIPPI standards for networking, system managers can integrate their Connection Machine system fully into today's heterogeneous supercomputing environments.

## 2.1 The Front-End Environment

The front-end computer is the user's gateway to the Connection Machine system. Through the front end, CM users develop, compile, debug, and execute their application programs. Administrators use the front-end computer to configure the Connection Machine system and to execute diagnostic programs for its maintenance; the CM OS offers interactive and automatic features for system administration.

The front-end computer's file system holds all system software and user programs for the Connection Machine system. (Data for user programs, on the other hand, is usually stored in the CM file system, which is discussed later in this chapter.) Programs execute in the front-end environment, with the front end passing instructions to the Connection Machine supercomputer, transmitting I/O requests to its associated I/O and display devices, and receiving program output and messages.

A front end is a multi-user UNIX system: either a Sun-4 Workstation that runs the SunOS operating system and contains a VMEbus, or a Digital Equipment Corporation VAX 8000 or 6300 series minicomputer that runs the ULTRIX operating system and contains a VAXBI I/O bus. Different types of front-end computers may be included in a single Connection

Machine system and may run applications simultaneously on that system. A Connection Machine system can have from one to four front ends.

## 2.2 Partitioning the Connection Machine System

A user process can access either the complete Connection Machine supercomputer or some portion of it. The portion accessed (whether the whole or the part) is called a partition. A partition is created and allocated for dedicated or multi-user use by a system process or user process giving an **attach** command. It is deallocated when the process detaches.

#### Flexibility for the Administrator

At any given time, a partition of a Connection Machine system can be available as a multi-user partition, a batch partition, or a single-user partition.

- A multi-user partition runs timesharing, and may run batch. Such a partition executes interactive programs for any number of users (up to an optional limit). If the administrator chooses, batch jobs from one or more batch queues may share resources with the interactive jobs, either at the same priority or at a different priority.

- A batch partition runs batch, but not timesharing. This partition is under the control of a batch queue. Interactive jobs may access the partition when no batch jobs are running. The batch queue, however, may be configured so that it detaches such users when the next batch job requires the partition.

- A single-user partition does not run timesharing, but may run batch. This type of partition is available either to one interactive user or to one interactive or batch user at a time.

Changing a partition among single-user, multi-user, and batch modes is as simple as starting or stopping a system process. It can be done interactively, or through scripts set to operate at particular times. Thus, an administrator might choose to divide a 32K system into one 16K multi-user partition and one 16K single-user partition for daytime use, but configure that same system as a single 32K batch partition on nights and weekends, with the changeovers occurring automatically at preset hours.

#### Flexibility for the User

A system administrator has the option of leaving the entire Connection Machine system in single-user mode. In this case, user programs dynamically partition the CM by attaching to and detaching from those portions of the machine required by their programs.

In other cases, users work within the partitioning established by the system administrator, choosing the multi-user partition or batch queue that best suits their needs.

| CM<br>Model | Number of<br>Processors | Possible<br>Partitions |

|-------------|-------------------------|------------------------|

| CM-2        | 64K                     | 16K, 32K, 64K          |

| CM-2        | 32K                     | 8K, 16K, 32K           |

| CM-2        | 16K                     | 8K, 16K                |

| CM-2a       | 8K                      | 8K.                    |

| CM-2a       | 4K                      | 4K                     |

## 2.3 The NQS Batch System

The Connection Machine uses the Network Queueing System (NQS) batch system, which is becoming standard for UNIX networks. This batch system supports two types of queues: batch queues, which are linked to a specific partition, and pipe queues, which feed jobs (via batch queues) to whichever partition is available to run them. It allows submission of batch jobs over the network, either via pipe queues or via **rsh**. It also allows the NQS manager to control the number and characteristics of available queues, as well as each queue's hours of operation.

The hours during which a batch queue executes jobs and the hours during which it accepts jobs are not necessarily identical. For example, a queue might accept jobs from 8 am till midnight, but execute jobs between 8 pm and 8 am. (A queue that accepts jobs is said to be *enabled*; one that executes jobs is said to be *started*.)

Creating and Configuring Queues. An NQS manager decides how many queues to create and what characteristics each queue will have, thus tailoring the batch system to the needs of the particular site. The administrator uses the qmgr utility to create each queue, naming and describing the queue and defining

- the hours during which the queue operates (queues with restricted hours start and stop automatically at designated times)

- the priority of this queue in relation to other queues

- the users or groups of users who can submit jobs to the queue

- time and size limitations for jobs executing from the queue

- the CM system resources available to jobs executing from the queue

- whether the queue has exclusive use of its sequencer(s) and whether it can forcibly detach other users

- whether a queue provides automatic attaches and detaches for its jobs

Submitting Batch Requests. Frequently, the NQS manager defines a number of queues with different characteristics. Users can then choose the queue most suitable for each program. In addition, users can further define the execution environment for a program by using options to the job submittal command that

- request that execution be delayed until a particular time

- request the use of a specified shell

- request that all environment variables be exported with the job

- direct the method by which output is to be handled

- set various per-process limits

- assign a priority to the job

Users can also ask for notification by mail of their job's progress, and can query the system for information on the characteristics and availability of queues and on the status of queued requests.

**Controlling Batch Queues.** NQS operators can start and stop queues, enable and disable queues, and shut down NQS. When necessary, they can also remove waiting and executing jobs from queues.

## 2.4 Timesharing

Each multi-user partition is a virtual machine environment, only slightly smaller than the physical environment, operating under the control of a timesharing executive. The executive arbitrates memory demands among user processes, switches the full CM context between processes, and swaps user processes to disk. Swapping to a DataVault — the recommended method — allows a speed of 25 megabytes per second (or 25 megabytes per second per DataVault for striped DataVaults). Administrators can tune timesharing parameters to best meet the needs of their sites; parameters include:

- the maximum number of processes that can execute simultaneously

- the minimum amount of time for which a process can be scheduled

- the maximum amount of memory any process will be allowed to consume

- the desired latency for the scheduler

- the amount of disk space to use for swapping

- the level of logging and the location of the log file

#### 2.5 The Program Development Environment

The program development environment available to Connection Machine users offers the full capabilities of the UNIX and X windows systems. In addition, it offers enhancements specific to CM parallel programming: parallel languages, specialized libraries, and programming tools. It also offers users access to two file systems: the front end's own UNIX file system and the UNIX-based, parallel, high-performance CM file system.

Users write programs in CM languages: C\*, CM Fortran, or \*Lisp. These languages are supersets of C, Fortran 77, and Common Lisp, respectively. Programs may also include code written in Paris (the Connection Machine's PARallel Instruction Set), and calls to specialized libraries, such as the Connection Machine Scientific Software Library (CMSSL).

Once the program is coded, it is compiled with a CM compiler. (Programs written in \*Lisp may be either compiled or interpreted.) Profiling options can be used during compilation, to allow profiling with the gprof command.

When a program is compiled, sequential code is translated directly to the native machine code of the front end. Source-level constructs that correspond to Connection Machine (data parallel) operations are translated to a mix of front-end machine code and instructions for the parallel processing unit. In typical programs, data structures are created in the Connection Machine memory and are used in precisely the same manner as structures in front-end memory. The difference is that operations on the Connection Machine structures can be carried out on many data items in parallel.

Debugging may be done either with a debugger resident on the front end or with **cmdbx**, the CM's parallel extension of the **dbx** debugger.

## 2.6 The Program Execution Environment

Program execution takes place, as mentioned above, either interactively or in batch mode. In either case, the program executes on the front-end computer and accesses the CM, its I/O subsystem, and its display hardware as needed. The program may access a DataVault, for example, either to read and write data, or to store the results of a checkpointing operation.

Several facilities — checkpointing, timing, and safety-checking — are available to aid program development and robustness during execution. In addition, tools are provided to allow programs executing on single-user partitions to initialize the partition.

#### Checkpointing

Many applications that run on the Connection Machine system require extended execution times, because of complexity, number of iterations, or both. Users need to be able to interrupt and later restart such a program: perhaps to allow it to run only when the system is not needed for other use, to allow for scheduled machine downtime or protect against unscheduled halts, or simply to allow for restarting the program from some intermediate state during debugging. The Connection Machine system supports this need with a checkpointing facility.

Checkpointing a program lets the user save (and later restart) an executable copy of a program's state. This includes the program's state on the front end, its state on the CM, a list of the files that the program had open at the time of the checkpoint, and a stored copy of the checkpointed program.

The CM checkpointing facility offers three basic methods of checkpointing:

- inserting checkpoints at particular points in a program

- having checkpoints occur periodically

- having a checkpoint occur when a program is sent a particular signal, such as the signal sent during a planned shutdown of the system

Checkpointing can be used from within a debugger, such as dbx, and it can be used on programs that execute only on the front end as well as on programs that use the CM.

#### Timing

A CM timer calculates, with microsecond precision, both the total elapsed front-end time (wall-clock time) and the total amount of time the CM is active. Calls to CM timers can be inserted anywhere in a program. A program can use (and nest) up to 64 timers for simultaneous coarse-grain and fine-grain timing.

#### Safety Checking

Users may choose to enable a CM safety-checking utility during program execution. This utility checks both for low-level errors and for inconsistencies in programs. Although safety checking reduces execution speed, it can be useful in developing and debugging programs.

## 2.7 The Connection Machine File System

The Connection Machine File System (CMFS) is designed to handle the immense amounts of data needed by many CM applications, to store data in a format most suitable for the parallel processing done by the CM, and to transform data between this parallel format and the serial format used by other systems.

#### **Serial and Parallel Formats**

A serial-format file consists of a single stream of data, suitable for processing by the front end or any other sequential computer. A parallel-format file contains many streams of data, one per Connection Machine virtual processor. It also contains geometry information indicating whether the many streams are to be organized as a multidimensional grid and, if so, how they are to be organized. CMFS library calls are available to transpose data from serial to parallel format, and vice versa. Thus, data can be exchanged between the Connection Machine system and other systems.

#### A UNIX-Like File System

The Connection Machine file system is closely modeled on the UNIX file system. It has a hierarchical directory structure, with directories and files identified by pathnames. Many CMFS user commands and library calls have counterparts in the UNIX file system that are similar in name and function. Users will thus find considerable congruence between their front end's file system and the CM file system, and will handle the two in very similar ways.

As in UNIX, any I/O device in the CM I/O system is regarded from the user's perspective as just another file in a file system. I/O to all devices in the Connection Machine system is handled in the same manner, regardless of the type of device involved. For example, writing data from the CM to a DataVault appears to be no different than writing to a tape drive. Users need to learn only a single set of commands and library calls to move data among all devices in the system.

## 2.8 CM Diagnostics

A complete set of diagnostics for the Connection Machine system is provided with Connection Machine software. Facilities are also provided to make it easy to send error reports and details of diagnostic failures through an electronic message network to the Customer Support Group at Thinking Machines Corporation.

# Part II Parallel Software

## Chapter 3

## Languages

Data parallel languages allow the programmer to organize data so that program operations may be applied to many elements of data at once. There are few differences in coding style between a data parallel program and a conventional serial program. In both cases a single sequence of instructions is used, with a serial control structure. However, parallel operations are performed on many data items at once. Thus the programming languages for the Connection Machine system provide parallel processing without requiring the programmer to indicate synchronization explicitly in programs.

Because the data parallel and serial programming styles are similar, they can use almost identical languages. The languages currently supported for the Connection Machine system are CM Fortran, C\* (pronounced *see-star*), and \*Lisp (pronounced *star-lisp*). CM Fortran implements the Fortran 90 array features directly. Each of the other two languages extends its corresponding serial language specification by adding a new data type. Very little new syntax is added; the power of parallelism arises simply from extending the meaning of existing program syntax when applied to parallel data.

CM Fortran and C\* are the most commonly used languages for numeric applications. \*Lisp is commonly used for artificial intelligence and other symbolic processing applications, but also provides excellent numerical performance with all the convenience and power of the Lisp language.

The following sections survey some broad themes, common to any data parallel programming language, that are useful to keep in mind when examining a language description.

## 3.1 Establishing Parallel Data Structures

Data parallel programs can be expressed in terms of the same data structures used in serial programs. Emphasis is on the use of large, uniform data structures, such as arrays, whose elements can be processed all at once. A statement such as  $\mathbf{A} = \mathbf{B} + \mathbf{C}$ , which in a serial language adds a single number **B** to a single number **C** and stores the result in **A**, can equally well indicate thousands of simultaneous addition operations if **A**, **B**, and **C** are declared to be arrays. The underlying paradigm is that every array element is in the memory of a different processor; if the number of array elements exceeds the number of physical hardware processors, a virtual processor mechanism transparently maintains the paradigm.

Although array declarations can thus in principle be identical for serial and data parallel programs, the underlying architecture may require careful allocation of array elements to physical processor memories for best performance. Indeed, in some cases very small arrays are better processed serially. Therefore, data parallel languages, like vector processing languages, generally provide some optional declarations that give the user control over data allocation. In CM Fortran, the compiler automatically determines, according to how the array is used in the program, whether an array should be considered serial or parallel, and how parallel arrays should be allocated to Connection Machine processors. The programmer can override such automatic decisions by inserting declarations in the form of structured comments. In C\*, the data types in a declaration implicitly specify whether a data structure is parallel. In \*Lisp, data structures are created dynamically, and the programmer uses different allocation operations to specify creation of serial or parallel data structures.

The choice of parallel data structures is perhaps the most important aspect of data parallel programming. Once data has been properly allocated, executable code follows naturally. It is not necessary to use different operation names for different cases. Parallel code can look just like serial code, in the same way that floating-point arithmetic looks like integer arithmetic. A conventional compiler examines the declarations of variables **B** and **C** to determine whether  $\mathbf{B} + \mathbf{C}$  will require an integer or floating-point add instruction. In the same way, a compiler for a data parallel language examines declarations to determine whether  $\mathbf{B} + \mathbf{C}$  will require a single addition operation or thousands.

### 3.2 Establishing Linkages among Data Elements

During the execution of a program, data from different problem elements are used together. Data parallel programs use pointers or array subscripts to establish connections between processors and hence between their data elements. An array of pointers, itself a parallel data structure, establishes an arbitrary pattern of intercommunication. If the required patterns are regular and local, such as processors sharing data with their nearest neighbors, then no explicit array of pointers is needed because each processor can easily calculate the address of its neighbors as needed (in some cases implicitly, with the assistance of special hardware such as the NEWS grid).

## 3.3 Establishing Scalar Data

Some data is not parallel. For example, it may be wasteful to place a copy of a constant permanently in every processor's memory since the constant can be efficiently broadcast as needed from a central point. For this reason, scalar data (whether constant or variable) may be declared as such and stored in the front end.

## 3.4 Operations on Mixed Data

Operations that use both scalar and parallel data typically involve replication or reduction. If a scalar value participates in an operation that yields a parallel result (such as adding a constant to every element of an array), the scalar value is replicated by broadcasting it to all processors at once. If parallel data participates in an operation that yields a scalar result, such as finding the sum of all of the elements of an array, a reduction operation is used; given one processor for each data element, such an operation can be completed very quickly by organizing the operations on the data into a balanced binary tree. (This organization is carried out by the underlying language implementation.)

## 3.5 Conditionals

Data parallel programs implement conditionals by limiting the impact of operations to a certain subset of processors, and hence to a subset of the data elements of a parallel data structure. A conditional operation first tests a specified condition in all elements of a parallel data structure, and then performs the operations only for array elements where the conditional was true. As in serial programs, conditionals may be nested in very general ways.

# Chapter 4 Fortran

Fortran for the Connection Machine system is standard Fortran 77 supplemented with the array-processing extensions of the ANSI and ISO (draft) standard Fortran 90. These extensions provide convenient syntax and numerous intrinsic functions for manipulating arrays.

Newly written Fortran programs can use the array extensions to express efficient data parallel algorithms for the CM. These programs will also run on any other system, serial or parallel, that implements Fortran 90. CM Fortran also offers several extensions beyond Fortran 90, such as the **FORALL** statement and some additional intrinsic functions. These features are well known in the Fortran community and are particularly useful in data parallel programming.

## 4.1 Structuring Parallel Data

Fortran 90 allows an array to be treated either as a set of scalars or as a first-class object. As a set of scalars, array elements must be referenced explicitly in a DO construct. In contrast, a reference to an array object is an implicit reference to all its elements (in undefined order). For example, to increment the elements of array A (100) by 1, a program can reference the array either way:

| A as a set                              | A as an   |

|-----------------------------------------|-----------|

| of scalars                              | object    |

| DO I=1,100<br>A(I) = A(I) + 1<br>END DO | A = A + 1 |

To operate on multidimensional arrays, DO loops must be nested to reference each element explicitly. In the statement  $\mathbf{A} = \mathbf{A} + \mathbf{1}$ , however,  $\mathbf{A}$  could be a scalar, a vector, a matrix, or a higher-dimensional array.

CM Fortran takes advantage of this standard feature when allocating arrays on the CM system. An array that is used only as a set of scalars is stored and processed on the front-end computer in the normal serial manner. Any array that is referenced as an object is stored in CM memory, one element per processor, and processed in parallel. In essence, the front end executes all of CM Fortran that is Fortran 77, and the CM executes all the array extensions drawn from Fortran 90. No new data structure is required to express parallelism.

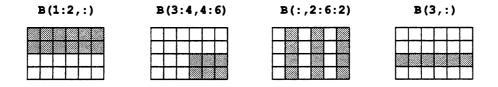

The simple array reference **A** is the default form of a *triplet subscript*, **A**(1:100:1), which resembles the control specification of a DO loop. Using triplet subscripts, you can replace DO loops with an array reference that indicates all the elements of interest — and thereby cause the array to be processed in parallel on the CM system.

An implicit triplet — that is, the array name alone — is usually used for whole arrays. You can, however, specify any of the control variables, just as in a DO loop, to indicate a *section* of the array. For example, some sections of array B(4,6) are:

Array sections can be used anywhere that whole arrays are used — in expressions and assignments and as arguments to procedures.

## 4.2 Computing in Parallel

The most straightforward form of data parallel computing is *elemental* computing, that is, operating on array elements all at the same time, each independently of the others. Any array assignment where the array is referenced as an object has this effect. For example, consider an assignment statement for a  $40 \times 40 \times 40$  array C:

$C = C^{**2}$

The CM system allocates one element of C in each of 64,000 processors, and all the processors operate on their respective elements of C at the same time.

An expression or assignment can involve any number of arrays or array sections, as long as they are all of the same shape. Scalars can be intermixed freely in array operations, since Fortran 90 specifies that a scalar is effectively replicated to match any array. For example, the following statement assumes that D and E are  $10 \times 10$  matrices and F is a  $10 \times 100 \times 100$  array:

$D = E^{*}2 + 1 + F(:, 1:10, 3)$

Another form of array operation uses an *elemental* intrinsic function. Fortran 90 extends most of the intrinsic functions of Fortran 77 so that they can take either a scalar or an array as an argument. If G is an array, this statement operates elementally:

$$G = SIN(G)$$

An array assignment can be performed conditionally if it is constrained by a WHERE statement. This statement includes a logical mask; it behaves like a DO loop with an embedded IF statement (except that the order in which elements are processed is undefined). For example, to avoid division by zero in an array assignment, one might say:

WHERE (D.NE.0) = E/D

Finally, CM Fortran offers a form of elemental array assignment, the FORALL statement, whose action is position-dependent. The syntax of a FORALL statement resembles a DO construct, but the assignments can be executed in parallel. For example, to initialize **H** as a Hilbert matrix of size **N**:

FORALL (I=1:N, J=1:N) H(I,J) = 1.0 / REAL(I+J-1)

**FORALL** can use a mask to make its action dependent on either the value or the position of the individual array elements. For example, to clear matrix  $\mathbf{H}$  below the diagonal, one can set a mask to select those positions where row index  $\mathbf{I}$  is greater than column index  $\mathbf{J}$ :

FORALL (I=1:N, J=1:N, I.GT.J) H(I,J) = 0.0

To initialize a table of integer logarithms:

FORALL (I = 1:10) LG (2\*\*(I - 1): 2\*\*I - 1) = I - 1

## 4.3 Communicating in Parallel

A second form of data parallel computing requires processors to access each other's memories, all at the same time. The pattern of interprocessor communication can be either regular (grid-based) or arbitrary. Fortran 90 defines a number of features that move data from one array position to another; these features map naturally onto the communication mechanisms implemented in CM hardware.

#### **Grid-Based Communication**

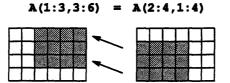

Many applications, such as convolutions and image rotation, need to move data in regular grid patterns. One way to specify such motion in Fortran 90 is by assigning array sections. For example, to shift vector values to the left:

To shift data on more than one dimension:

3

Fortran 90 also defines intrinsic functions that perform grid-based data motion. The function CSHIFT performs a circular shift of array elements, and EOSHIFT performs an end-off shift. For example, the following statement shifts the elements on the second dimension of A by one position to the left and assigns the result to B. (The SHIFT argument can also be an array, which shifts the rows by different offsets.)

B = CSHIFT(A, DIM=2, SHIFT=1)

For solving differential equations, CM Fortran programs can access a library of *stencil* routines. These routines combine pipelined floating-point arithmetic with highly optimized grid communications, often in several directions at once. The communication patterns are customized to the various stencil, or star, patterns of the finite difference discretizations of these equations. For example, the two-dimensional, five-point stencil routine gets data from four grid neighbors and performs four adds and five multiplies; it achieves speeds considerably beyond those achieved by manual coding of the same operations.

#### **General Communication**

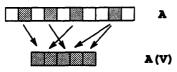

Processors must communicate in arbitrary patterns to map an unstructured problem onto a grid or to index into arbitrary locations of an array. To perform these operations in parallel, CM Fortran provides vector-valued subscripts and **FORALL**.

A vector-valued subscript is a form of array section that uses a vector of index values as a subscript. If **A** is a vector of length 10 and **P** is a permutation of the integers from 1 to 10, then  $\mathbf{A} = \mathbf{A}(\mathbf{P})$  applies this permutation to the values in **A**. The statement  $\mathbf{A}(\mathbf{P}) = \mathbf{A}$  applies the inverse permutation.

The index values can be repeated, which causes element values to be repeated in the section. For example, if V is the vector (/2, 6, 4, 9, 9/), then A(V) is a five-element vector whose values are A(2), A(6), A(4), A(9), and A(9), in that order:

The **FORALL** statement provides the same arbitrary indexing into an array of any rank. For example, the following statement uses the two-dimensional index arrays X and Y to permute the values of a two-dimensional array **B**:

FORALL (I=1:N, J=1:M) C(I,J) = B(X(I,J), Y(I,J))

### 4.4 Transforming Parallel Data

Fortran 90 defines a rich set of intrinsic functions that take an array argument and construct a new array (or scalar). All these transformational functions take only array objects (not arrays subscripted in the Fortran 77 manner), and all are therefore computed in parallel on the CM.

One set of transformational functions is the reduction intrinsics, such as SUM or MAXVAL. These functions apply a combining operator to the elements of an array (or array section) and return the result as a scalar. For example, given a 100 x 500 matrix D, the following expression returns the sum of the elements in the upper left quadrant:

SUM( D(1:50,1:250) )

These functions can take a mask argument to make the reduction conditional. If applied only to a specified dimension, they return an array of rank one less than the argument array. For example, given the 100 x 500 matrix D, the following expression returns a 100-element vector containing the sums of the positive elements in each row.

SUM( D, DIM=2, MASK=D.GT.0 )

A parallel-prefix, or *scan*, operation applies a combining operator cumulatively along a grid dimension, giving each element the combination of itself and all previous elements. These operations, which are useful in such algorithms as line-of-sight and convex-hull, can be expressed with the **FORALL** statement and a reduction function. For example, in the

following add-scan (or sum-prefix) operation, each element of B gets the sum of all elements up to and including the corresponding element of A:

FORALL (I=1:N) B(I) = SUM(A(1:I))

The array construction functions transform arrays in a wide variety of ways. For example, **TRANSPOSE** performs matrix transposition; **RESHAPE** constructs a new array with the same elements as the argument but a different shape; **PACK** and **UNPACK** behave as gather/scatter operations; and **SPREAD** replicates an array along a new dimension. CM Fortran also provides the Fortran 90 array multiplication functions, **DOTPRODUCT** and **MATMUL**. In addition to the standard Fortran 90 intrinsics, CM Fortran also offers the functions **DIAGONAL**, **REPLICATE**, **RANK**, **PROJECT**, **FIRSTLOC**, and **LASTLOC**.

## 4.5 To Learn More

To learn more about programming in Fortran on the Connection Machine, see *Getting* Started in CM Fortran, from the Connection Machine documentation set, and Implementing Fine-Grained Scientific Algorithms on the Connection Machine Supercomputer, Technical Report #TR 90-1.

34

•

# Chapter 5 The C\* Language

C\* is an extension of the C programming language designed to support data parallel programming.

The C\* language is based on the standard version of C specified by the American National Standards Institute (ANSI). C programmers will find most aspects of C\* code familiar to them. C language constructs such as data types, operators, structures, pointers, and functions are all maintained in C\*; new features of ANSI C such as function prototyping are also supported. C\* extends C with a small set of new features that allow programmers to use the Connection Machine system efficiently.

C\* is well suited for applications that require dynamic behavior, since it allows the size and shape of parallel data to be determined at run time. In addition, it provides programmers with all the standard benefits of C, such as block structure, access to low-level facilities, string manipulation, and recursion. C\* also provides a straightforward method for calling Paris functions and CM Fortran subroutines from a C\* program, thus allowing access to these languages when appropriate.

## 5.1 Structuring Parallel Data

In C<sup>\*</sup>, data is allocated on the CM only when it is tagged with a *shape*. A shape is a way of logically configuring parallel data. C<sup>\*</sup> includes a new construct called *left indexing* that is used in declaring a shape. The left index provides the number of dimensions (or *axes*) in the shape and the number of *positions* along each dimension. Positions correspond to processors (or virtual processors) on the CM. For example,

shape [256][512]s;

declares a shape s that is laid out as a 256 x 512 grid on the CM.

This shape is considered to be *fully specified*, since the number of dimensions and positions are provided at compile time. Shapes may also be partially specified or fully unspecified. C\* lets the programmer dynamically allocate and specify shapes, thus providing flexibility in the way they can be used.

Once a shape has been fully specified, one can declare *parallel variables* of that shape. Parallel variables have both a standard C data type and a shape. For example, the code

```

shape [16384]t;

int:t parallel_int1, parallel_int2;

float:t parallel_float1;

```

declares three parallel variables of shape t; each consists of 16384 *elements*, laid out along one dimension. Parallel variables interact most efficiently when they are of the same shape. In addition to the above method, parallel variables can also be allocated dynamically.

C\* also provides parallel versions of arrays and structures. For example, the code

```

shape [16384]t;

int:t parray[16];

```

declares a parallel array, parray, which consists of 16 parallel ints of shape t. The code

```

shape [16384]t;

struct scalar_struct {

int a;

float b;

};

struct scalar_struct:t pstruct;

```

declares a parallel structure, **pstruct**, that consists of the standard C structure **scalar** struct replicated in each of the 16384 positions of shape t.

C\* includes pointers to both shapes and parallel variables. As in standard C, C\* pointers are fast and powerful.

4

## 5.2 Computing in Parallel

#### Parallel Use of Standard C Operators

C\* extends the use of standard C operators, through overloading, to apply to parallel data as well as scalar data. For example, if **p1**, **p2**, and **p3** are all parallel variables of the same shape, the statement

p3 = p2 + p1;

performs a separate addition of the values of p1 and p2 in each position of the shape, and assigns the result to the element of p3 in that position. The additions take place in parallel. If p1 or p2 were not a parallel variable, it would first be promoted to parallel, with its value replicated in every element. Note that this line of code looks exactly like standard C; the result differs, however, depending on whether the variables are parallel or scalar.

#### The with and where Statements

C\* adds new statements to standard C that allow operations on parallel data.

The with statement selects a current shape. In general, parallel variables must be of the current shape before parallel operations can take place on them. For example, code like the following is actually required to perform a parallel addition like the one shown above:

```

shape [16384]t;

int:t p1, p2, p3;

with (t)

p3 = p2 + p1;

```

C\* also adds a where statement to restrict the set of positions on which operations are to take place; the positions to be operated on are called *active*. Selecting the active positions of a shape is known as *setting the context*. The where statement in the following example ensures that division by 0 is not attempted:

```

with (t)

where (p1 != 0)

p3 = p2 / p1;

```

Serial code always executes, no matter what the context.

Programs may contain nested where statements; these cumulatively shrink the set of active positions. The context is passed into functions called within the scope of a where statement and is correctly reestablished when returning to an outer level as a result of a break, continue, goto, or return statement. Note that the context does not affect the flow of control of a program. One can still use standard C statements such as if and while to manipulate flow of control.

C\* extends the standard C **else** statement for use in conjunction with the **where** statement; using **else** after a **where** reverses the set of active positions. The new **everywhere** statement makes all positions active.

#### New Operators and Data Type

$C^*$  adds a few new operators to standard C. For example, the <? and >? operators are available to obtain the minimum and maximum of two variables (either scalar or parallel).

C\* also includes a new single-bit data type called **bool**. Using parallel **bools** for flags can save space, since memory in the CM may be allocated on bit, rather than byte, boundaries.

### **Parallel Functions**

Functions in C\* can pass and return parallel variables and shapes. If it is not known what the current shape will be when the function is called, you can use the new keyword current in place of a specific shape name within the function declaration; current always means the current shape.

A useful feature of C\* is *overloading* of functions. C\* allows you to declare more than one version of a function with the same name — for example, one version for scalar data and another for parallel data. The compiler automatically chooses the right version.

## 5.3 Communicating in Parallel

C\* provides two methods of parallel communication: as part of the syntax of the language and via an extensive library of functions. Both allow communication in regular patterns within shapes and in irregular patterns both within and between shapes. Regular communication is faster. ŧ

#### **Regular Communication**

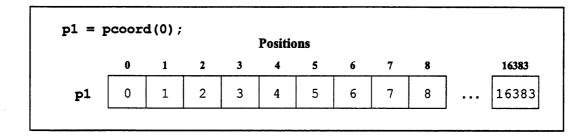

C\* uses the intrinsic function pcoord to provide a self-index for a parallel variable along a specified axis of its shape. For example, if **p1** is of a one-dimensional shape with 16384 positions (and the shape is current), pcoord initializes **p1** as shown in Figure 4:

Figure 4. The use of pcoord with a one-dimensional shape

The pcoord function is typically used to provide regular communication — called *grid* communication in  $C^*$  — along the axes of a shape. For example, the following code sends values of **source** to the elements of **dest** that are one coordinate higher along axis 0:

[pcoord(0) + 1]dest = source;

In the common case where **pcoord** is called within a left index expression, and the argument to **pcoord** specifies the axis indexed by the left index, C\* allows a shortcut: the call to **pcoord** can be replaced by a period. Thus, for a two-dimensional shape, the following provides grid communication along both axis 0 and axis 1:

[. + 1][. - 2]dest = source; (A chess knight's move)

Wrapping from one end of an axis to the other is provided by a standard C\* programming idiom that involves the use of **pcoord** along with the new modulus operator %% and the **dimof** intrinsic function, which returns the number of positions along an axis of a shape.

Library functions are also available to perform grid communication. For example, the to\_grid\_dim and to\_grid functions can be used in place of the statements above.

#### Irregular Communication

C\* uses the concept of left indexing to provide communication between different shapes, as well as within-shape communication that does not necessarily occur in regular patterns.

A left index can be applied to a parallel variable. If the index itself is a parallel variable, the result is a rearrangement of the values of the parallel variable being indexed, based on the values in the index. If the index is of one shape and the parallel variable being indexed is of another shape, the result is a remapping of the parallel variable into the shape of the index. Thus, in the following code,

```

dest = [index]source;

```

the parallel variable dest gets values from source; the values in index tell dest which element of source is to go to which element of dest. The variables dest and index must be of the current shape; source can be of any shape. This is known as a get operation. Putting the index variable on the left-hand side specifies a send operation. Sends are roughly twice as fast as gets. The operations can also be performed with the send and get functions in the C\* communication library. (These are closely related to the Paris operations of the same name.)

## 5.4 Transforming Parallel Data

C\* provides operators and library functions that enable programmers to easily perform common transformations of parallel data.

C<sup>\*</sup> overloads the meaning of several standard C compound assignment operators to provide a succinct way of expressing global reductions of parallel data. For example, +=, when applied as a unary operator to a parallel variable, sums the values of all active elements of the parallel variable. The resulting value can be treated the same way as the result of a serial operation. Similarly, the |= operator performs a bitwise OR of all elements of a parallel variable. The **reduce** and **global** library functions provide similar capabilities for various operations.

The C\* communication library contains many functions that perform other transformations of parallel data. For example:

- The scan function calculates running results for various operations on a parallel variable.

- The spread function spreads the result of a parallel operation into elements of a parallel variable.

- The **rank** function produces a numerical ranking of the values of parallel variable elements; this ranking can be used to rearrange the elements into sorted order.

÷

# Chapter 6

## The \*Lisp Language

The \*Lisp language is an extension of Common Lisp used to program the Connection Machine system in a data parallel style. It allows users to write Connection Machine programs that make full use of the Connection Machine hardware, yet at the same time retain the clarity, expressiveness, and flexibility of Lisp.

The \*Lisp language extends the Common Lisp language by providing parallel equivalents for the basic operations of Common Lisp, along with operations that are unique to data parallel programming, such as processor selection, parallel prefix, interprocessor communication, and data shape specification.

A \*Lisp program is simply a Common Lisp program that includes calls to \*Lisp operators. \*Lisp is thus fully compatible with the Common Lisp standard; programs written in Common Lisp will run unmodified in \*Lisp. A call to a \*Lisp operator on the front-end machine causes all active processors on the CM to execute that operation in parallel. Sequential Common Lisp code, running on the front end, can be freely intermixed with parallel operations; only parallel operations are executed on the CM.

With few exceptions, \*Lisp functions and macros are defined via defun and defmacro, just as in Common Lisp. \*Lisp programs are compiled by the Common Lisp compiler, which is extended to recognize and handle \*Lisp operations. \*Lisp programs can therefore be written, compiled, and tested with the same editors and debuggers as Common Lisp programs.

## 6.1 Structuring Parallel Data

#### **Scalar and Parallel Data**

\*Lisp distinguishes between data stored on the front-end computer and data stored in parallel on the CM. Because \*Lisp is an extension of Common Lisp, it includes all the standard Common Lisp data types. These data types are all stored in the memory of the front-end machine and are collectively referred to as *scalar* data. \*Lisp also supports an additional, parallel, data type called a *pvar*, which is always stored on the Connection Machine. Pvars are collectively referred to as *parallel* data.

A pvar is a *parallel* variable, that is, a single variable with a separate, modifiable value in each processor of the CM. Operations performed on a pvar are performed by all active processors simultaneously, with each processor seeing and modifying only its own value for the pvar. For most of the scalar data types available in \*Lisp, there are corresponding pvar data types. The eight basic pvar data types are boolean, integer, floating-point, complex, character, array, structure, and front-end reference.

#### Creating Pvars in \*Lisp

There are three basic ways to create, or *allocate*, a pvar in \*Lisp, each designed to serve a specific purpose, as shown in the examples below:

```

(!! 5) ;; Allocating a temporary pvar

(*defvar my-five-pvar 5) ;; Allocating a permanent pvar

(*let ((my-pi!! pi)) ;; Allocating a local pvar

(*!! 2 my-pi!!))

```

The simplest way to allocate a pvar is via the \*Lisp function !! (pronounced *bang-bang*), which takes a single scalar value as its argument, and returns a temporary pvar with that value in every processor. For example, the expression (!! 5) above returns a pvar with the value 5 in each processor. Most functions in \*Lisp operate this way, performing a parallel operation and then returning a temporary pvar value.

One can also allocate a pvar via **\*defvar**, which defines a *permanent* pvar, a pvar allocated in such a way that it will remain in existence until it is explicitly *deallocated* by the user. The example above defines a permanent pvar named **my-five-pvar**, and

2

initializes it to have the value 5 in every processor. (Note that scalar values are automatically promoted to pvars where necessary.)

It is also possible to allocate *local* pvars that exist only for the duration of a body of \*Lisp code. By analogy with the Common Lisp operators let and let\*, \*Lisp includes two operators, \*let and \*let\*, which are used to define these kinds of pvars. The example above defines a local pvar named my-pi!!, and then multiplies its value by 2 in every processor.

#### Defining the Shape of the Data

The shape of the data stored in a pvar is determined by the grid of processors that the CM is currently simulating. The CM can be configured to simulate a grid of processors with up to 31 dimensions, although a one-, two-, or three-dimensional grid is often sufficient. The CM can also simulate more than one grid at a time. The defining property of a processor grid is its *geometry*, which specifies the rank of the simulated grid and the sizes of its dimensions.

The combination of a particular grid geometry and a set of pvars that share that geometry is called a *virtual processor* set (VP set). A VP set is simply a description of a particular abstract configuration of the CM processors, combined with a set of associated pvars that use that configuration. For example, the expression

(def-vp-set my-vp-set '(32 64))

defines a new VP set named my-vp-set with a two-dimensional geometry of 32 x 64 processors.

\*Lisp uses the concept of a *current VP set* to determine which VP set is active. Unless otherwise specified, all pvar operations take place within the current VP set. However, you need not concern yourself with defining VP sets if you choose not to. There is a *default VP set* that is automatically defined whenever you start up \*Lisp, and until you create and select other VP sets, all pvar operations take place within this default VP set.

\*Lisp provides operations to allocate VP sets of many types. The simplest such operator is def-vp-set, which allows you not only to define a VP set, but also to specify one or more permanent pvars that will be associated with that VP set. For example, the expression

defines a new VP set named double-my-vp-set with twice as many processors as in the my-vp-set example above. This new VP set has two associated permanent pvars: an unsigned integer pvar x, and a single-precision floating-point pvar y.

An important feature of the simulated grids defined by VP sets is that they permit the assignment of *addresses* to processors. There are two basic methods used to assign addresses to processors on the CM: *send addressing* and *grid addressing*.

Each processor has a unique numeric *send address* based upon its location within the physical hardware of the CM. The \*Lisp operation (**self-address**!!) returns a pvar whose value in each processor is the send address of that processor.

Each processor also has a grid address, a sequence of coordinates that defines its position in the *n*-dimensional grid of processors the CM is currently simulating. The \*Lisp operation (self-address-grid!! n) returns a pvar whose value in each processor is the coordinate of that processor along the nth dimension of the current grid.

#### Accessing and Copying Parallel Data

The most basic pvar operations provided by \*Lisp allow you to access pvar values on a per-processor basis, to copy the value of one pvar into another, and to display the elements of a pvar over a range of processors.

The standard function for reading the value of a pvar in a single processor is **pref**. For example, (**pref my-pvar 10**) returns the value of **my-pvar** in processor 10.

The macro **\*setf**, analogous to the Common Lisp macro **setf**, is used in combination with **pref** to set the value of a pvar in a specific processor, as in (**\*setf** (**pref my-pvar** 10) 123), which stores the quantity 123 into processor 10 of **my-pvar**.

It is also possible to refer to processors by grid addresses using the \*Lisp operator grid, as in (\*setf (pref my-pvar (grid 5 7)) 111), which stores the quantity 111 into my-pvar at grid location (5,7).

The contents of one pvar may be copied into another by using the assignment operator **\*set**. For example, (**\*set pvar1 pvar2**) copies the contents of **pvar2** into **pvar1** in all active processors. **\*set** is often used to set the value of a pvar in all processors. For example, the statement (**\*set pvar1 5**) will store the value 5 into **pvar1** in all active processors.

You can use the \*Lisp operation **ppp** (short for **pretty-print-pvar**) to display the values of a pvar. For example, the expression (**ppp** (**self-address**!!) : **end** 20) displays the send addresses of the first 20 processors:

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

The keyword argument : end is used to control how many values are printed. The ppp operator provides many keyword arguments that specify the arrangement and format of the pvar values that are displayed.

## 6.2 Computing in Parallel